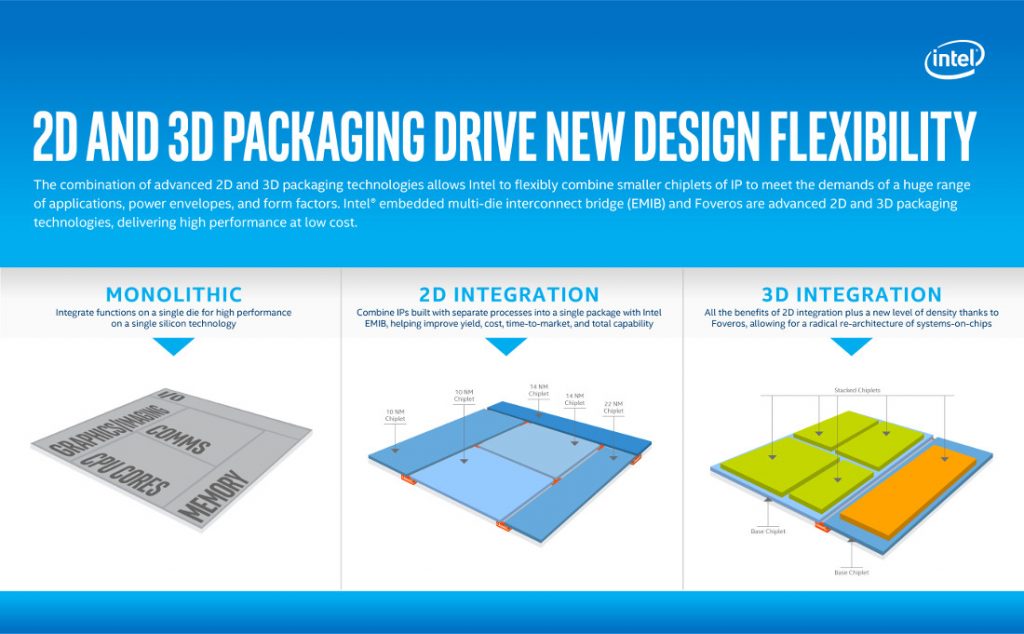

Intel at the Architecture Days 2018, has revealed the CPU core roadmaps through 2021 which includes the next generation of integrated graphics, the future of Intel’s graphics business, new chips built on 3D packaging technologies, and even parts of the microarchitecture for the 2019 consumer processors.

For the high-performance Core architecture, Intel has three new codenames over the next three years. These are the code names for the individual core microarchitecture, not the chip. Sunny Cove is built on 10nm and will come to market in 2019 and offer increased single-threaded performance, new instructions, and ‘improved scalability’.

Next up, the Sunny Cove will have AVX-512. These cores, when paired with Gen11 graphics, will be called Ice Lake. Willow Cove looks to be a design for 2020, most likely also on 10nm. Intel lists the highlights here as a cache redesign, new transistor optimizations, and additional security features, likely referring to further enhancements from new classes of side-channel attacks.

Golden Cove; the round of trio will firmly come in 2021 and we’re likely to see it on 10nm and or 7nm. Golden Cove is where Intel adds another slice of the serious pie onto its plate, with an increase in single threaded performance, a focus on AI performance, and potential networking and AI additions to the core design. However, the lower-powered Atom microarchitecture roadmap is on a slower cadence than the Core microarchitecture.

The upcoming microarchitecture for 2019 is called Tremont, which focuses on single threaded performance increases, battery life increases, and network server performance. It will be a 10nm design. Next up is Gracemont, which Intel lists as a 2021 product. Intel lists that Gracemont will have additional single threaded performance and a focus on increased frequency. As said above, these are just the microarchitecture names. The actual chips these cores are in will likely have different names, which means a Lake name for the Core microarchitecture. The future microarchitectures are likely to be uncoupled from any process technologies.