JEDEC Solid State Technology Association has officially published JESD209-6, the latest specification for Low Power Double Data Rate 6 (LPDDR6) memory. Tailored for mobile, AI, and high-performance applications, LPDDR6 brings a major leap in memory bandwidth, power efficiency, and reliability features.

The LPDDR6 standard defines the essential requirements for a JEDEC-compliant x24 single-channel SDRAM, with device densities ranging from 4 Gb to 64 Gb. It covers the full memory architecture — from signal assignments and packaging to AC/DC characteristics — aiming to meet the rising demands of next-gen devices.

Key Features of LPDDR6

High-Speed Architecture

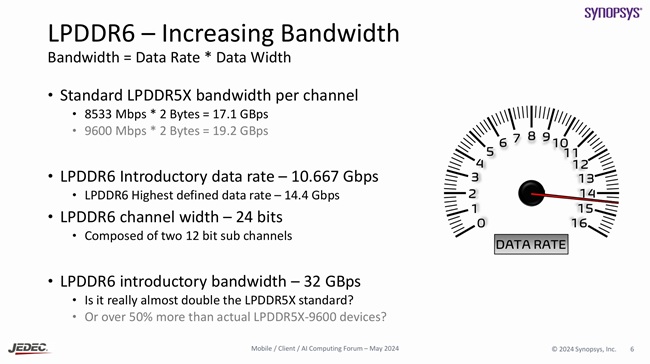

LPDDR6 is built to support faster AI and compute workloads with a dual sub-channel architecture that enables better bandwidth utilization. Core highlights include:

- Two sub-channels per die with 12 DQ lines each

- Four command/address (CA) signals per sub-channel to reduce pin count

- Burst lengths of 32B and 64B, selectable dynamically

- Static efficiency mode to boost performance in high-capacity setups

- Dynamic NT-ODT (Non-Target On-Die Termination) to fine-tune signal quality in real time

Based on a 2024 presentation by JEDEC and Synopsys, LPDDR6 may offer data rates as high as 14.4 Gbps, outstripping LPDDR5X’s 10.667 Gbps limit and targeting 32 GB/s bandwidth.

Power Efficiency Enhancements

Designed with mobile and edge computing in mind, LPDDR6 reduces energy use with several hardware-level optimizations:

- Lower VDD2 voltage supply for reduced operating power

- DVFSL (Dynamic Voltage Frequency Scaling – Low Power) to scale voltage down during light usage

- Dynamic Efficiency mode using a single sub-channel for low-bandwidth scenarios

- Alternating clock command inputs to balance performance and power

- Support for partial self-refresh and active refresh to minimize energy spent on idle memory maintenance

Improved Security & Data Reliability

To address growing system reliability demands, LPDDR6 includes multiple mechanisms for safeguarding memory operations:

- Per Row Activation Counting (PRAC) to monitor and maintain data integrity

- Carve-out Meta Mode for reserving secure memory zones

- Built-in ECC (Error Correction Code) and programmable link protection

- Support for CA parity, error scrubbing, and MBIST (Memory Built-In Self Test)

Availability

LPDDR6-based memory products are expected to debut in late 2025, though JEDEC has not confirmed a specific launch timeline.

Speaking on the release, Mian Quddus, JEDEC’s Chairman of the Board of Directors, said:

JEDEC is proud to introduce LPDDR6, the culmination of years of dedicated effort by members of the JC-42.6 Subcommittee for Low Power Memories. By delivering a balance of power efficiency, robust security features, and high performance, LPDDR6 is an ideal choice for next-generation mobile devices, AI, and related applications to thrive in a power-conscious, high-performance world.